The Anatomy of a GNU Makefile

Why was the Makefile always so confident? Because it knew it could always “make” things happen!

In the dynamic world of software development, optimizing the build process is key to managing intricate projects. The Makefile stands out as a robust tool that significantly streamlines this process. In this article, we will delve into the structure and purpose of a Makefile, showcasing how it has revolutionized my own build process. By abstracting complex dependencies, the Makefile allows me to focus solely on the specific parts of the software I am currently working on, eliminating unnecessary distractions. Let's explore the anatomy of a Makefile and provide a basic example.

Understanding the Makefile

At its core, a Makefile is a script that automates the building of a software project. It consists of rules, dependencies, and actions to be executed. Makefiles are widely used in compiling code, managing dependencies, and organizing complex projects.

Components of a Makefile

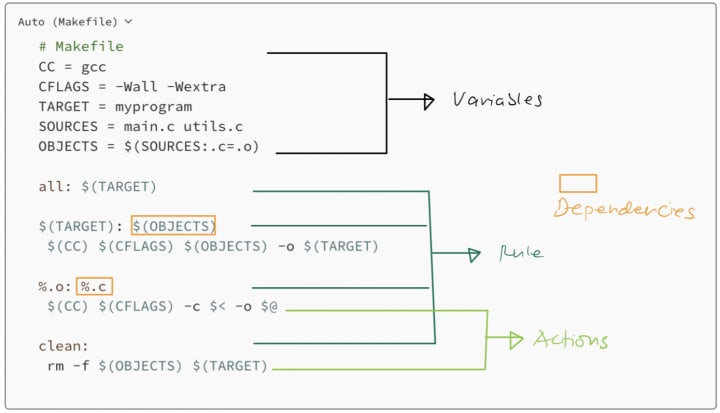

Here’s a simple example of a Makefile for compiling a C program:

Variables: Makefiles commonly define variables to store values that can be reused throughout the file. Variables can hold compiler commands, flags, file names, and more. They make it easy to update values in a centralized location, ensuring consistency across the build process. In the example above, these are the variables and their associated functions:

- CC: Represents the compiler used

- CFLAGS: Represents the compiler flags. -Wall -Wextra enables all warnings and extra warnings

- TARGET: Represents the target executable

- SOURCES: Represents the source files

- OBJECTS: Represents the object files generated from source files, obtained by replacing the “.c” extension with “.o” for each source file.

Rules: Rules define targets, dependencies, and actions to be performed. Each rule specifies the steps needed to build a target, such as compiling source code or linking object files. In the example above, these are the rules.

- all: Represents the default rule or target

- %.o: Represents a pattern rule for object files. It specifies how to compile individual source files into object files.

- clean: Represents a rule to clean the generated object files and the target executable. The action is to remove these files using the rm command.

Dependencies: Dependencies represent the files or targets that need to be present or up-to-date before executing a rule. Makefiles use dependencies to determine the order of execution and avoid unnecessary rebuilds. If a dependency is modified, the associated rule will be triggered.

- $(OBJECTS) is a dependency of $(TARGET)

- (%.c) the source file is a dependency of the object file (%.o)

Actions: Actions are the commands executed when a rule is triggered. They specify the actions required to build the target, such as compiling source files, linking object files, or running additional scripts. The actions in the Makefile are the lines starting with a tab character. They define the commands to be executed when the corresponding rules are triggered.

Conclusion

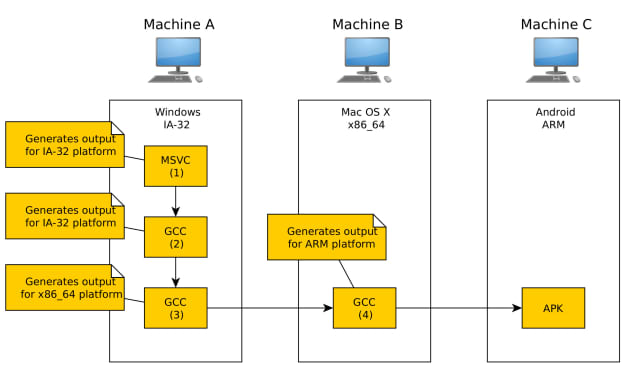

By incorporating Makefiles into your projects, it becomes a breeze for software developers to compile code, manage dependencies, and steer clear of tedious recompilations. With practice, you can even elevate the capabilities of your Makefiles to effortlessly handle advanced scenarios like conditional builds, cross-compilations, parallel execution, and seamless integration with other tools. So go ahead, and take a well-deserved vacation while Makefiles work their magic for you!

Comments

There are no comments for this story

Be the first to respond and start the conversation.