Could This Report Be The Definitive Answer To Your ANALYSIS AND DESIGN OF INTEGRATED CIRCUITS: FIELD PROGRAMMABLE GATE ARRAYS?

This is a report presentation for Computer Engineering (COE-624) Analysis of Integrated Circuits - Field Programmable Gate Arrays.

Intended Learning Outcome (ILO)

Discus and Explain the:

1. Field Programmable Gate Arrays

- Historical Perspective

2. Programming Technologies .

3. Architectures

- PALs

- PLDs

- CPLDs, and

- FPGAs including Programmable logic, Interconnect network, I/O buffers, and Specialized core.

1. Historical Perspective

1. Programmable Logic Arrays ~ 1970

- Implement any set of sum Implement any set of sum-of-products logic equations products logic equations .

- Incorporated in VLSI devices .

It was the Texas Instruments or TI, coined the term Programmable Logic Array. Very-large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining hundreds of thousands of transistors or devices into a single chip.

2. Programmable Logic Devices ~ 1980

- MMI Programmable Array Logic (PAL)

- 16L8 – combinational logic only

- 16R8 – sequential logic only

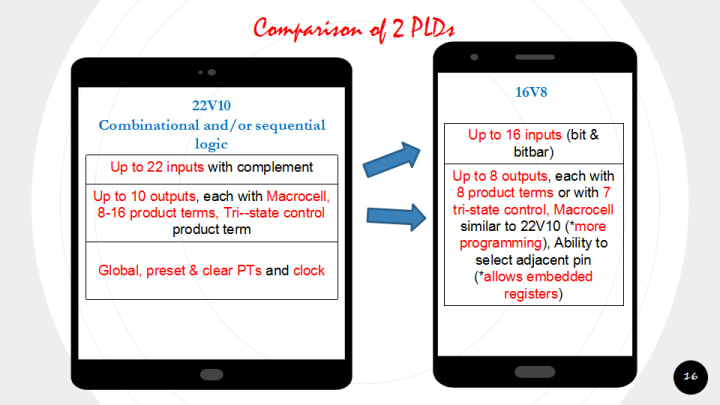

- AMD 22V10 and Lattice 16V8

- Complex PLDs – arrays of PLDs with routing network

MMI stands for Monolithic Memories, Inc. AMD introduced the 24-pin 22V10 PAL. Advanced Micro Devices (AMD) acquired by Lattice Semiconductor in 1999.

3. Field Programmable Gate Arrays ~ 1985

- Xilinx Logic Cell Array (LCA)

Xilinx headquarters in the San Jose, California, United States. Xilinx is an American technology company, primarily a supplier of programmable logic devices.

4. CPLD & FPGA architectures became similar ~2000

- Incorporation of RAMs and other specialized cores

- Programmable system-on-chip

2. Programming Technologies

1. PLAs were mask programmable

- Texas Instruments or TI developed a mask-programmable IC based on IBM. The TMS2000 had up to 17 inputs and 18 outputs with 8 JK flip flop for memory.

A programmable logic array (PLA) has a programmable AND gate array, which links to a programmable OR gate array, which can then be conditionally complemented to produce an output. Programmable Logic Array (PLA) is a fixed architecture logic device with programmable AND gates followed by programmable OR gates. PLA is basically a type of programmable logic device used to build reconfigurable digital circuit. PLA is a combination of memory and logic.

- A programmable logic array should not be confused with Programmable Array Logic (PAL), in which both AND and OR gates are programmable.

PLA is similar to a ROM in concept; however, it does not provide full decoding of variables and does not generate all minterms as in the ROM. Though its name consists of the word "programmable", it does not require any type of programming like in C and C++.

2. PALs used fuses for programming

A programmable array logic (PAL) devices have arrays of transistor cells arranged in a "fixed-OR, programmable-AND" plane used to implement "sum-of-products" binary logic equations for each of the outputs in terms of the inputs and either synchronous or asynchronous feedback from the outputs.

Comparison (Programmable Array Logic & Programmable Logic Array)

Comparison with other Programmable Logic Devices:

- PLA has programmable AND gate array and programmable OR gate array.

- PAL has programmable AND gate array but fixed OR gate array.

- ROM has fixed AND gate array but programmable OR gate array.

3. Early PLDs & CPLDs used floating gate technology

- Erasable Programmable Read Only Memory (EPROM)

- Ultra-violet erasable (UVEPROM)

- Electrically erasable (EEPROM)

- Flash memory came later and was used for CPLDs

A PLD or programmable logic device is an electronic component that is used to build digital circuits that are re-programmable. A programmable logic device does not have a defined function once manufactured, unlike a logic gate, and has to be programmed before it can be used.

A PLD is a combination of a logic device and a memory device. The memory is used to store the pattern that was given to the chip during programming. Most of the methods for storing data in an integrated circuit have been adapted for use in PLDs. These include:

- Silicon antifuses

- SRAM

- EPROM or EEPROM cells

- Flash memory

PLDs have an undefined function at the time of manufacturing, but they are programmed before made into use.

4. FPGAs used RAM for programming

5. Later trends

- Fuses were replaced with anti-fuses

- Better reliability

- Large CPLDs went to RAM-based programming

6. RAM

- Volatile - must configure after power-up

- In-System Re-programmable (ISR)

- Run-Time Reconfiguration (RTR)

- dynamic reconfiguration while system is operating

Random Access Memory (RAM):

- Write/Read operations

- Volatile: Data is lost when power is turned off

RAM is a volatile type of memory, meaning that its contents are lost each time the power is switched off.

7. Floating gate technologies

- UV EPROM, EEPROM, and flash memory

- EEPROM and flash memory

- Flash memory

EPROM (Erasable Programmable Read Only Memory)

- Can be erased using Ultraviolet Light

- Electrically Erasable PROM (EEPROM or E 2 PROM)

- Like an EPROM, but erased with an electrical signal

An EPROM cell is a MOS (metal-oxide-semiconductor) transistor that can be switched on by trapping an electric charge permanently on its gate electrode. This is done by a PAL programmer.

Flash memory is non-volatile, retaining its contents even when the power is switched off. It can be erased and reprogrammed as required. This makes it useful for PLD memory.

8. Fuse/anti Fuse

- Non-volatile but not re-usable

- One Time Programmable (OTP)

Non-Volatile: Data is permanent.

Fuse/anti-fuse: Programmable only once.

- They are called anti-fuses because they work in the opposite way to normal fuses, which begin life as connections until they are broken by an electric current.

3. Architectures

- PALs

- PLDs

- CPLDs, and

- FPGAs including Programmable logic, Interconnect network, I/O buffers, and Specialized core.

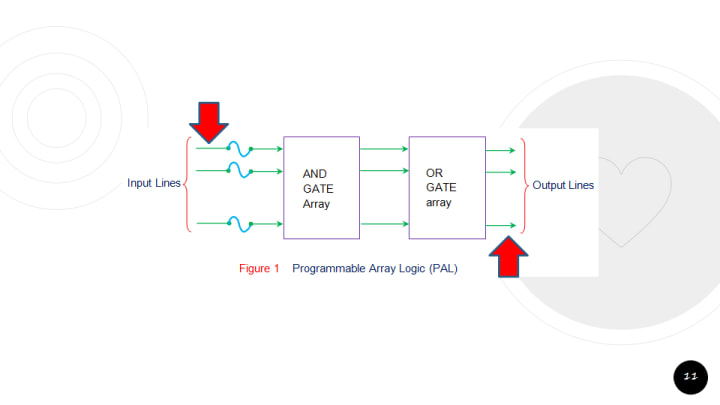

Programmable Array Logic (PLA)'s is the most commonly used type of programmable logic device (PLD ). The special feature of PAL is that it has a programmable AND array and a fixed OR array. Since PALs are easily manufacturable and less expensive, PALs are popular in practical applications.

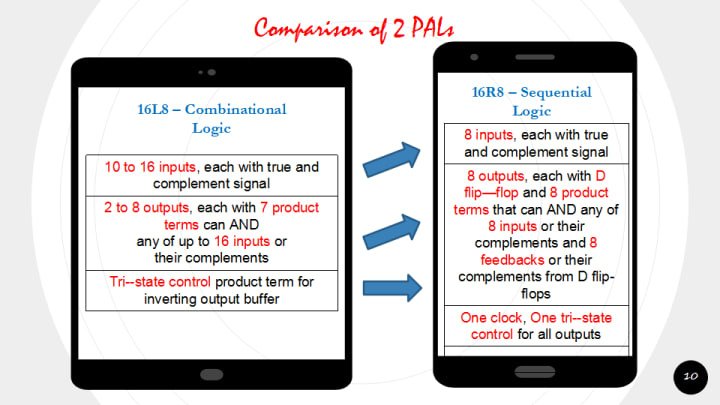

Comparison of two (2) PALs

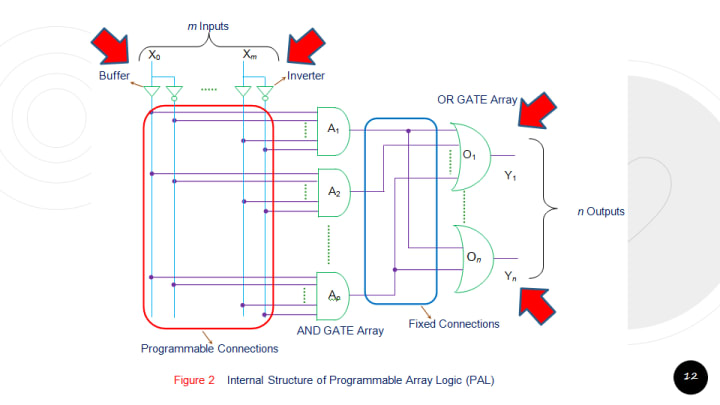

Figure 2 shows the internal structure of a PAL with m inputs and n outputs. Each of the input lines is showed to pass through the buffers and/or inverters. All of these inputs are connected each and every AND gate present in the PAL.

Applications

Programmable Logic Device (PLD)s programmed by a user is called a field-programmable. Advanced Micro Devices (AMD) acquired by Lattice Semiconductor in 1999. Users can also specify the desired connections and supply the information to the manufacturer. The manufacturer prepares an overlay that is used to complete the connections as the last step in the fabrication process. Such PLDs are called mask programmable.

Two (2) kinds of PLDs

Comparison of two (2) PLDs

Internal Structures of PLD

Applications

Advantages PLA/PAL vs. PLD

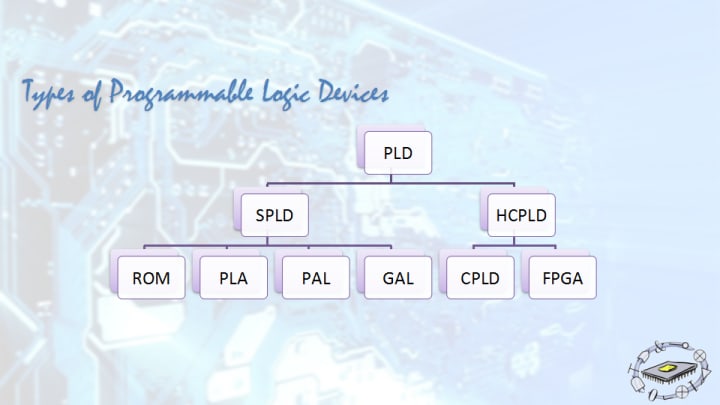

Types of Programmable Logic Devices

Acronyms

- PLD - Programmable Logic Device

- SPLD - Simple Programmable Logic Device.

- HCPLD - High Capacity Programmable Logic Device

- ROM - Read Only Memory

- PLA - Programmable Logic Array

- PAL - Programmable Array Logic

- GAL - Generic Array Logic

- CPLD - Complex Programmable Logic Device

- FPGA - Field Programmable Gate Array

If you want to use my report presentation, feel free to download it here.

References

Andres, K. (1970). A Texas Instruments Application Report: MOS programmable logic arrays. Texas Instruments. Bulletin CA-158. Report introduces the TMS2000 and TMS2200 series of mask programmable PLAs.

Greer, D. L. (!972). Electrically Programmable Logic Circuits US Patent 3,818,452. Assignee: General Electric.

Pellerin, D., & Holley, M. (1991). Practical Design Using Programmable Logic. Prentice-Hall. p. 15. ISBN 0-13-723834-7.

Like what you read?

Send me a gift to help contribute to my future endeavor.

Thank you.

About the Creator

Domingo Añasco-Gaces Samontina, Jr.

.Professional Member of the Mechatronics and Robotics Society of the Philippines

.Certified Documented Information Controller with TUV Rheinland Qualifications

.Master of Science in Engineering (on-going) with Professional Teacher Certificate

Comments

There are no comments for this story

Be the first to respond and start the conversation.